LA 1 Modul 1

Percobaan 1B

- Panel DL 2203C.

- Panel DL 2203S.

- Jumper.

- Laptop.

- Software Proteus ver minimal 8.17

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian [Kembali]

Pada rangkaian diatas terdapat beberapa gerbang logika yang digunakan. Masing masing gerbang logika memiliki prinsip kerja yang berbeda.

- Gerbang NOT

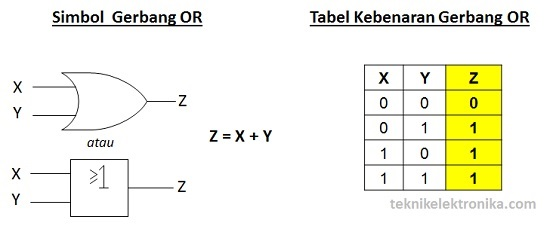

- Gerbang OR

A. Gerbang

Logika

Praktikum percobaan

gerbang logika ini menggunakan dua buah input utama, yaitu B0 dan B1. Kedua

input tersebut kemudian dihubungkan ke beberapa rangkaian gerbang logika dasar,

sehingga menghasilkan keluaran pada terminal H1 sampai dengan H7.

Setiap keluaran

merepresentasikan jenis gerbang logika yang berbeda. H1 terhubung dengan

gerbang NOT sehingga menghasilkan sinyal kebalikan dari input yang diberikan.

H2 terhubung dengan gerbang AND, sehingga keluarannya bernilai logika 1 hanya

jika kedua input bernilai 1. H3 terhubung dengan gerbang OR yang memberikan

keluaran logika 1 apabila salah satu atau kedua input bernilai 1. H4 terhubung dengan gerbang XOR yang

menghasilkan keluaran logika 0 jika kedua input sama, baik sama-sama 0 maupun

sama-sama 1. Pada jalur berikutnya, H5 menggunakan NAND yang memberikan

keluaran logika 1 apabila salah satu atau kedua input bernilai 0. H6

menggunakan NOR yang memberikan keluaran logika 0 apabila salah satu atau kedua

input bernilai 1, dan H7 menggunakan XNOR yang menghasilkan keluaran logika 1

jika kedua input sama, baik sama-sama 0 maupun sama-sama 1.

Prinsip kerja

dari percobaan ini adalah dengan memberikan kombinasi input B0 dan B1, yaitu

00, 01, 10, dan 11, kemudian mengamati perubahan keluaran pada setiap gerbang

logika.

B. Aljabar

Boolean

Rangkaian pertama

menghasilkan keluaran H1. Input B dan D terlebih dahulu diproses oleh gerbang

XOR sehingga menghasilkan keluaran logika 0 jika kedua input sama, baik

sama-sama 0 maupun sama-sama 1. Sementara itu, input A, C’, dan D diproses

melalui gerbang AND tiga masukan, hasil dari gerbang ini akan berlogika 1 jika

ketiga inputannya bernilai 1. Kedua hasil dari gerbang kemudian digabungkan

menggunakan gerbang OR sehingga keluaran H1 akan bernilai 1 apabila salah satu

atau dari kedua gerbang memiliki keluaran 1. Persamaan logika dari rangkaian

kedua dapat dituliskan sebagai H1 = (B ⊕ D) + (A · C’ · D).

Rangkaian kedua

menghasilkan keluaran H2. Sama seperti pada rangkaian H1, input B dan D

terlebih dahulu diproses oleh gerbang XOR sehingga menghasilkan keluaran logika

0 jika kedua input sama, baik sama-sama 0 maupun sama-sama 1. Perbedaannya

terletak pada bagian bawah rangkaian, di mana input A, B’, dan C diproses

melalui gerbang AND tiga masukan. Hasil dari gerbang ini akan bernilai logika 1

hanya apabila ketiga input bernilai 1. Kedua hasil dari gerbang kemudian

digabungkan menggunakan gerbang OR sehingga keluaran H2 akan bernilai 1 apabila

salah satu atau dari kedua gerbang memiliki keluaran 1. Persamaan logika dari

rangkaian kedua dapat dituliskan sebagai H1 = (B ⊕ D) +

(A · B’ · C).

Download File Rangkaian (klik disini)

Download Video Rangkaian (klik disini)

Download Datasheet OR (klik disini)

Download Datasheet AND (klik disini)

Download Datasheet NOT (klik disini)

Download Datasheet NOR (klik disini)

Download Datasheet NAND (klik disini)

Download Datasheet XOR (klik disini)

Download Datasheet XNOR (klik disini)

Komentar

Posting Komentar